이제 본격적으로 반도체 공정파트로 들어가보자. 여러 기업 반도체 공정관련 회사들을 지원할때 매우 핵심적인 개념들이다.

반도체를 만드는 공정은 전공정과 후공정 파트가 이 두가지 공정을 들어가기 전에 이 과정은 어디서 이루어질까?

바로 입자, 온도, 습도, 실내 공기압 등이 제어되는 밀폐된 공간이다. 이곳을 우리는 Clean Room이라고 부른다.

여기서는 앞으로 배울 Photo공정에 광학적 영향을 덜 주는 노란색 파장이 나오는 곳에서 작업을 한다. 참고로 노란색과 빨간색은 장파장이다. 따라서 단파장이 제거된 곳에서 작업을 한다고 이해한다면 쉽다.

빛 뿐만아니라 Clean Room에서는 공조과정이 천장과 바닥에서 이루어져 입자들을 철저하게 제어한다.

1입방피트당 0.5um입자의 개수를 Clean Room별로 분석해놓은 것을 class라고 부른다. class가 낮아질수록 가격은 비싸지고 삼성전자나 sk하이닉스는 class100 정도에서 이루어진다.

좀 더 자세하게 Clean Room구조를 살펴보자. 크게 Clean Room은 공정엔지니어들이 근무하며 설비의 모니터만 확인할 수 있는 Production bay와 설비엔지니어들이 근무하는 Service chase가 있다. Service chase에서는 설비를 고쳐야하는 경우가 많으므로 지하에 있는 경우도 있고 class1000으로 비교적 입자에 대한 제어가 느슨한반면 Production bay는 직접적은 공정을 모니터로만 제어한다는 대목만 봐도 class1이라는 이유가 타당해 보인다.

반도체 공정이 Clean room에서 이루어졌다면 실제 공정이 이루어지는 Si 반도체 판을 Wafer라고 한다. Si는 95%비율로 함양되어 있다. 그렇다면 여기서 핵심적으로 기억해야할 것은 무엇일까? Wafer는 해가 거듭할수록 직경과 두께가 증가하고 있다는 것이다. Wafer를 크게 만들어야 그 안에 들어갈 die수를 최대한으로 늘릴 수 있다. 단순히 칩이 작아지니까 Wafer도 작아지고 있겠지 라고 오해하는 일이 없어야겠다. 참고로 현재의 wafer크기는 2020년기준 18인치(450mm)웨이퍼를 양산검토중에 있다.

두께와 직경이 늘어나면 생산성(throughoutput)이 늘어나지만 수율(yield)은 저하된다.

생산성(throughoutput) : 시간당 처리가능한 wafer의 개수

수율(yield) : 성공한 die수/설계한 die수

이 둘은 tradeoff 관계이지만 생산성을 늘리는 방향으로 wafer는 가고 있다.

예를 들어 하나의 wafer에서 100개의 칩을 생산할 수 있고 97%의 수율을 가졌다고 해도 10000개의 칩을 생상할 수 있고 95%의 수율을 갖는 것이 훨씬 이득이기 때문이다.

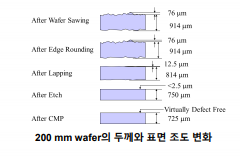

이러한 wafer의 제작과정은 Si의 정제 - 순수한 Si덩어리뽑기(ingot) - slicing 과정을 거친다. ingot시에는 Czochralski 방식과 Float-zone방식이 있는데 Czochralski 방식이 저비용과 큰직경이 가능하고 심지어 재사용이 가능하여 많이 사용된다. Float-zone방식은 고순도를 요구하는 전력 device에서만 주로 요구한다. 한장씩 썰어내는 slicing 과정이 끝나면 wafer 제조가 끝난 것이 아니다. 평탄도와 표면조도를 맞추는 수없이 많은 절차가 필요하다. 이러한 과정중에 분명히 두께는 얇아질 것이므로 이를 예상하여 wafer 제조 업체들은 목표두께보다 두껍게 해서 수요 업체에 넘긴다. 이 수많은 절차들에 대해 우리는 전공정으로 분류하는 것이다.

Wafer에는 격자 구조의 방향을 표시하는 trimming이 필요하다. 일종의 이름표같은 것이다. 150mm이하에는 Flat zone방식을 택하고 있고 200mm이상에는 Notch type을 택하고 있다.

slicing 뒤에 일어나는 wafer제작과정을 간단하게만 알아보자. 크게 순서는 edge rounding-lapping-ethching-polishing-inspection 이다.

edge rounding의 목적은 응력의 집중분산과 열응력 저항 분산이다. 이를 통해 particle 파손과 격자손상을 400% 완화할 수 있다.

이후에 일어나는 lapping-etching-polishing-inspection 은 순서대로 평탄도맞추기-손상제거하기-표면조도맞추기-검사하기 정도로만 생각하고 있자. 결국 완성된 wafer라 하면 원하는 두께, 조도가 요구에 맞게 맞춰진 것이다.

'반도체 > 전공정 이론' 카테고리의 다른 글

| [14] 공정 관련 기초 6, 도핑공정 세정공정 (2) | 2020.11.10 |

|---|---|

| [13] 공정 관련 기초 5, 포토공정, Etch공정 (0) | 2020.11.10 |

| [12] 공정 관련 기초 4, Oxidation CVD ALD PVD (0) | 2020.11.09 |

| [11] 공정 관련 기초 3, 진공 플라즈마 (0) | 2020.11.08 |

| [10] 공정 관련 기초 2 (1) | 2020.11.07 |